LoRaWAN CSMA Configuration levels (Go back)

LMIC_CSMA_LEVEL 1 :

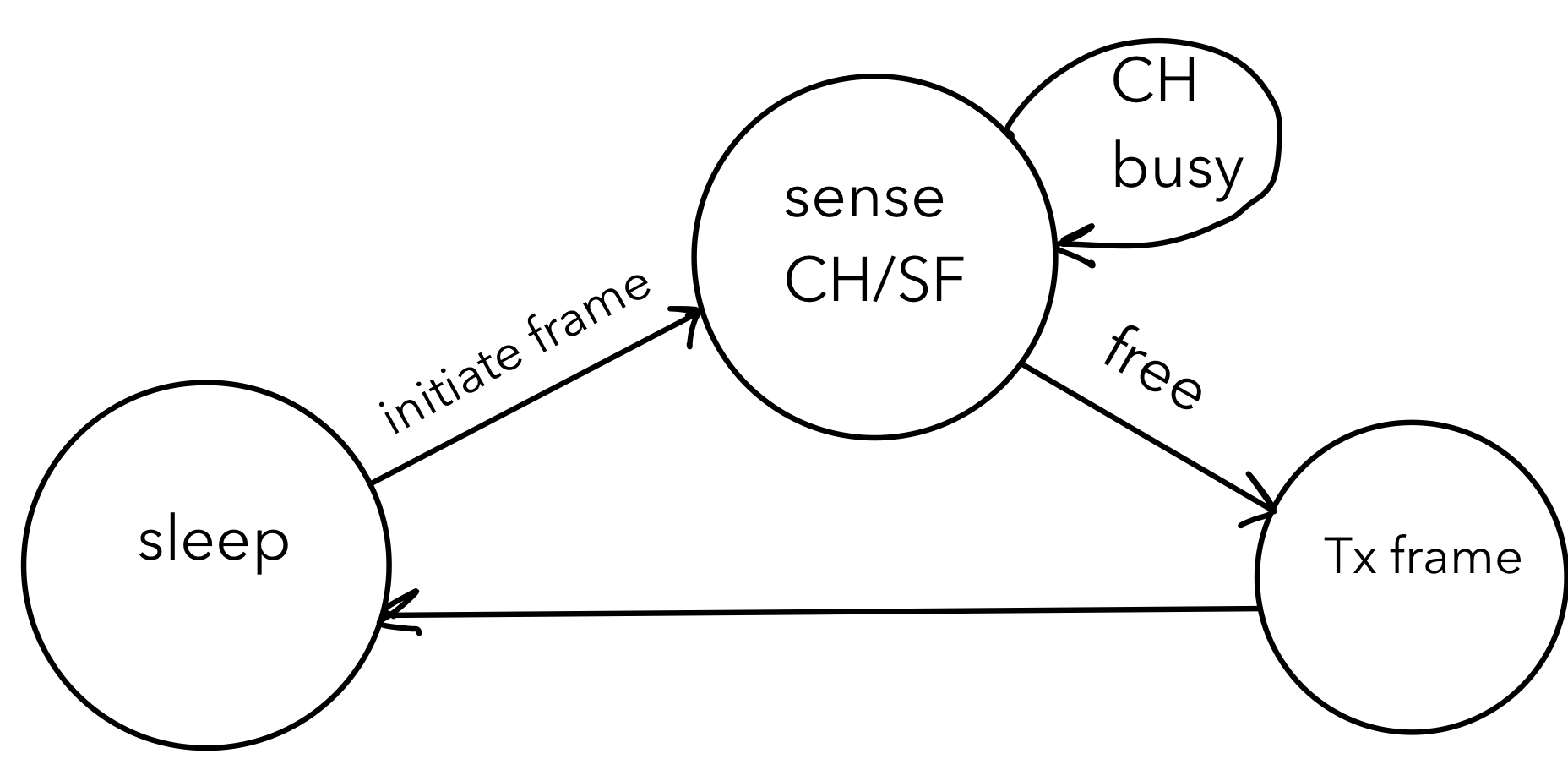

Under this configuration, a LoRa node first senses the chosen CH/SF combination for on-going transmissions for a DIFS duration.

During a DIFS window a random number of CAD operations are executed.

A free channel is classified as "free" upon a cleay DIFS window. I.e., when all of the randomly selected CAD operations report a free channel.

The number of CADs to perform is randomly selected while 20 is set at maximum.

To assume a free channel, a clear DIFS window is mandatory.

This means that all CADs performed within the DIFS window must inform the channel is free.

If an on-going transmission is detected, under LMIC_CSMA_LEVEL 1 the node waits till the channel is free prior to transmitting the frame.

The following state diagram highlights possible states a LoRa node may undergo prior to making a transmission under this setting.

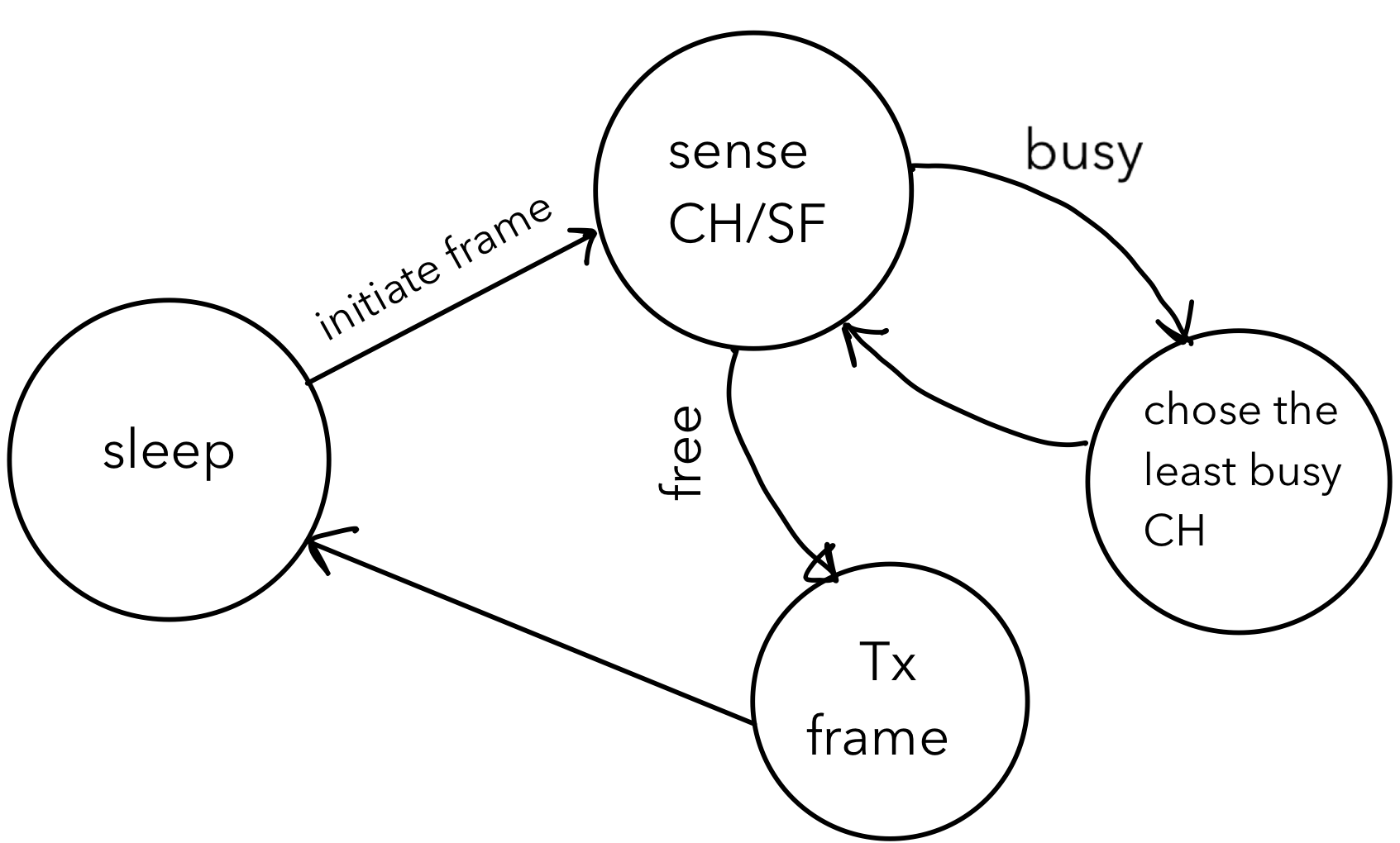

LMIC_CSMA_LEVEL 2 :

This option performs the channel sensing as per LMIC_CSMA_LEVEL 1 but allows a node to hop randomly to a different channel upon sensing a busy CH/SF.

If an on-going transmission is detected, the node switches to a randomly selected channel and senses the same for on-going CH/SF transmissions.

Should the newly selected CH is sensed free, the frame is transmitted.

Otherwise, the process repeats.

The list of channels available for random selection are from the eight user defined channels.

The following is a state diagram highlighting possible states a LoRa node may go through prior to making a transmission under this setting.

LMIC_CSMA_LEVEL 3 :

This option enables opportunistic channel profiling. Under this setting, a node maintains an "occupancy matrix" representing the busyiness of 8 channels. In other words, the occupancy matrix is a record of a nodes' own historical interactions with channels. When a channel is sensed busy, the node searches through this matrix and opts for the least bussiest channel. This mechanism as opposed to random channel selection yields faster results under higher network contensions.